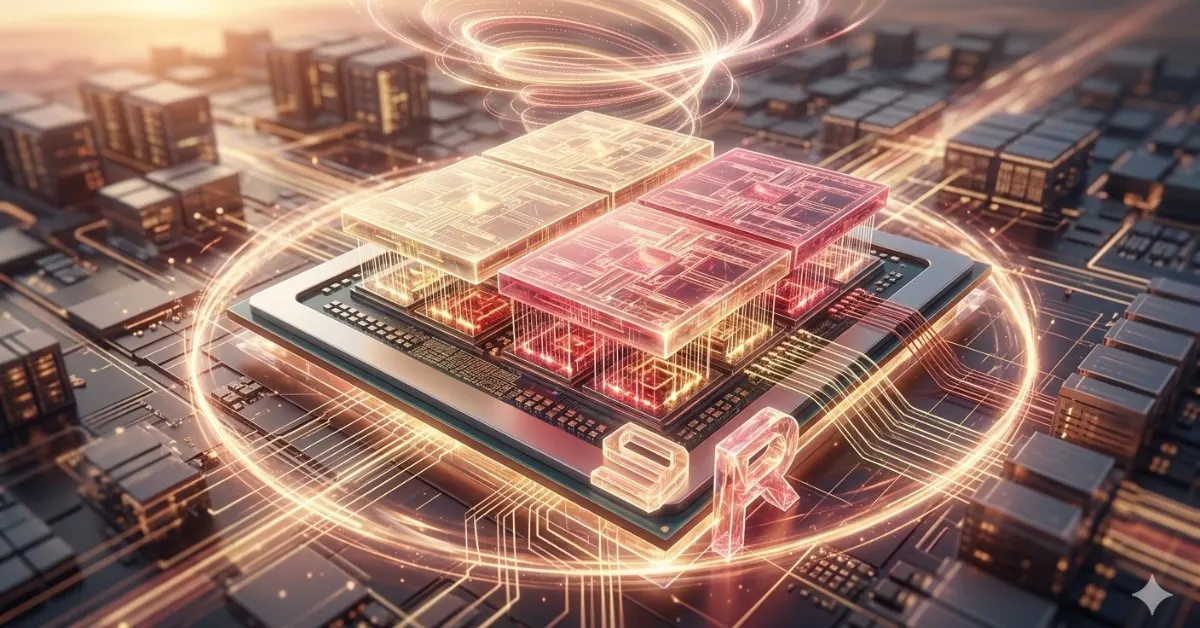

Taiwan Semiconductor Manufacturing Co. (TSMC) in April 2026 detailed its next-generation A16 process technology, introducing backside power delivery as a key architectural change for advanced chips. The announcement, made during the company’s technology symposium, sets out a roadmap for improved performance and power efficiency in future processors used across artificial intelligence, data centers and mobile devices. The update matters now because chipmakers are approaching physical limits in conventional scaling, forcing changes at the architectural level rather than relying solely on smaller transistors.

Backside power delivery moves power routing beneath the transistor layer

The A16 node incorporates what TSMC calls backside power delivery, a design approach that shifts power routing to the underside of the wafer. By separating power and signal routing, the company says the design reduces electrical interference and improves efficiency. This differs from conventional frontside routing, where both power and signal lines share limited space, creating congestion as transistor density increases.

TSMC indicated that the approach is designed to deliver gains in both performance and energy efficiency compared with its earlier N2 process. While the company did not publish all detailed figures in its initial briefing, it described measurable improvements in speed and power consumption enabled by reduced resistance and better current distribution. The move aligns with a broader industry shift toward new chip architectures as traditional scaling under Moore’s Law slows.

Target markets include AI accelerators and mobile processors

The A16 process is positioned for high-performance computing and mobile applications, with particular emphasis on AI accelerators. These workloads require dense transistor layouts and efficient power delivery, making them a primary target for backside power architectures. TSMC said the node is expected to enter production in the coming years, though it did not specify exact volume timelines in the announcement.

Industry observers have pointed to increasing demand from AI chip designers as a key driver behind such developments. Companies building large-scale compute infrastructure are pushing foundries to deliver higher efficiency per watt, not just raw performance. In mobile devices, the same principles apply at a smaller scale, where battery constraints make power efficiency a defining factor.

The introduction of A16 also reflects competitive pressure in the semiconductor sector, where rivals are pursuing similar innovations in packaging and power delivery. The distinction now lies less in node naming and more in how effectively each manufacturer integrates new techniques into mass production. For TSMC, the challenge will be translating the architectural shift into reliable yields at scale.

What follows is a transition period in which chip designers must adapt their layouts to take advantage of backside power delivery. That adjustment will influence how quickly the technology moves from announcement to widespread adoption. If successful, A16 could mark a turning point where architectural innovation, rather than pure transistor shrinkage, becomes the main driver of semiconductor progress.